Systemy Wbudowane, Laboratorium

2021-03-05

Na tych laboratoriach zrobimy pierwsze kroki w kierunku pisania programów w języku VHDL. Jest to język opisu sprzętu Hardware Description Language – HDL, który pozwala na stworzenie modelu działania komponentów cyfrowych i weryfikację jego poprawności.

Wykonaj kroki opisane w sekcji Hello world program na tej stronie. Przeanalizuj ten kod, postaraj się znaleźć analogie do innych znanych Ci języków programowania.

Spróbuj odszukać źródła biblioteki

textio(używa jej program z poprzedniego zadania). Przeanalizuj źródła i spróbuj dopisać do poprzedniego programu możliwość odczytania linii z klawiatury i wypisaniu jej z powrotem.

make build.make r=hello_world.Wykonaj kolejne kroki ze strony, z sekcji Full adder module and testbench. Ponownie przeanalizuj kod pierwszego i drugiego programu.

make build.make wave r=adder_tb.Słowa kluczowe:

ENTITY — określa sposób komunikacji, wejście i wyjście naszego układuARCHITECTURE — określa zachowanie układu (behaviour)PROCESS — zawarta w ARCHITECTURE lista kroków określająca konkretny programCOMPONENT — deklarowany w ARCHITECTURE odwołuje się do niższego w hierarchii komponentu, ENTITYPORT — wejście lub wyjście dla danego układuCo to jest adder i jak działa?

Adder jest to komponent w układzie liczącym sumę dwóch liczb binarnych. Na wejściu dostajemy cyfry dwóch liczb binarnych oraz tzw. carry, który zawiera nadwyżkę z dodawania cyfr niżej (overflow). Dodajemy zadane cyfry wraz ze wspomnianą nadwyżką. Na wyjście podajemy cyfrę wyniku wraz z kolejną nadwyżką, jeżeli taka nastąpiła.

W jaki sposób jest testowany sumator?

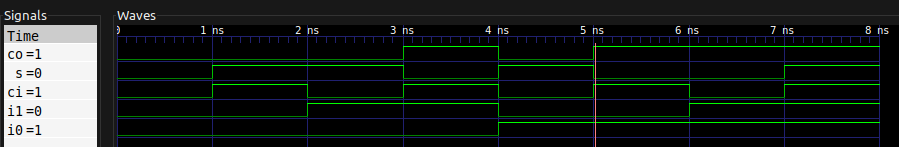

Sumator jest „wpinany” w testbench poprzez stworzenie nowej instancji komponentu. Dzięki temu jesteśmy w stanie komunikować się z naszym adder-em. Następnie określamy wszystkie możliwe wejścia wraz z wszystkimi możliwymi wyjściami adder-a. Na wejściu mamy trzy różne bity, więc mamy możliwych kombinacji. Po kolei sprawdzamy, czy nasze predykcje zgadzają się z faktycznym wynikiem danym przez adder. Za każdym razem czekamy jedną nanosekundę, czyli wszystkie porty adder-a będą widoczne przez jedną nanosekundę.

Uruchom program

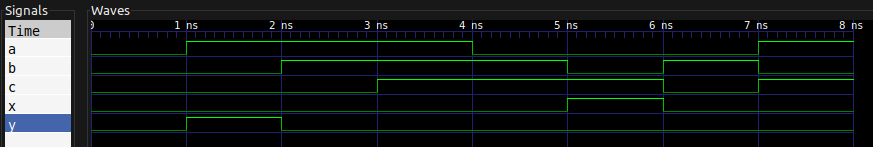

gtkwavez wygenerowanym plikiem przebiegów (adder.ghw). Zbadaj przebiegi sygnałówi0,i1,ci,s,co.

Jak powyżej zostało wspomniane — każda kombinacja utrzymuje się przez jedną nanosekundę. Wykres przedstawia binarny stan każdego z portów podczas wszystkich testów.

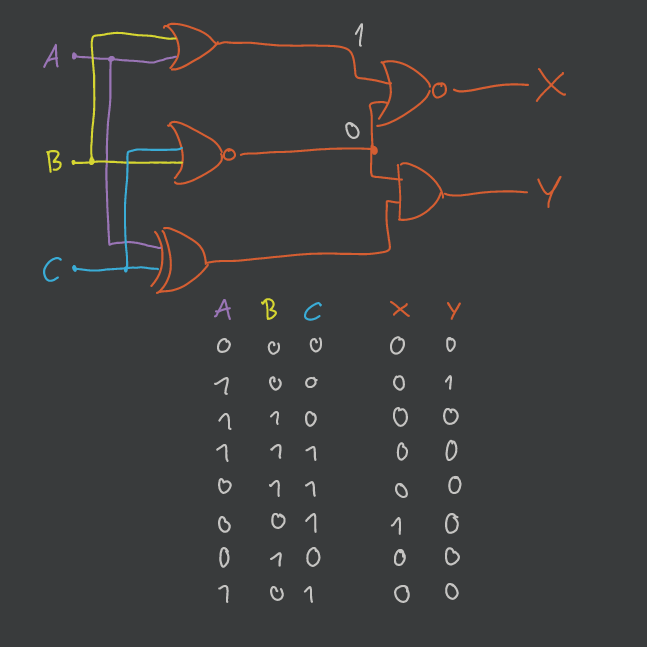

Bazując na zdobytej wiedzy, napisz kod jednostki i testujący dla następującego układu logicznego:

Analiza ręczna układu:

make build.make wave r=ex4_tb.Wynik programu GTKWave: